# Les familles TTL ALS et AS

La série SN 54/74, apparue en 1965, peut être considérée comme le point de départ de l'arborescence technologique bipolaire, et jouit, encore aujourd'hui, d'une grande popularité, fondée tout à la fois sur des performances séduisantes et un caractère économique hérité de la maîtrise de productions en grand volume.

Un deuxième pas a été franchi, cinq ans plus tard, en direction d'une grande vitesse, alliée à de plus hautes performances, avec l'introduction de la série Schottky (S), qui utilise les diodes dites de « clamping ». Et de récentes innovations dans le concept des circuits ont rendu possible le développement de deux nouvelles familles appelées AS (Advanced Schottky) et ALS (Advanced Low Power Schottky).

La famille AS améliore la rapidité de la série Schottky dans un rapport deux, et la puissance dissipée dans le même rapport suivant les types. Privilégiant d'abord le facteur vitesse, avec un temps de propagation par porte de 1,5 ns, la série AS peut se substituer à certaines familles réalisées en technologie rapide ECL, génération ECL 10 000 comprise.

La série ALS améliore, quant à elle, à la fois la vitesse et la consommation dans un rapport deux par rapport aux circuits de la famille LS (Low Power Schottky). Elle offre un temps de propagation de 4 ns et une dissipation de 1 mW par porte, et peut remplacer avec avantage certaines familles logiques plus lentes et à plus forte dissipation, et éventuellement certains circuits C-MOS.

# Deux concepts pour une technologie rapide

Mais revenons sur la technologie choisie pour développer les familles AS et ALS.

Cette technologie repose sur deux concepts de base qui, associés et intégrés au niveau de la cellule élémentaire du circuit, ont permis d'obtenir de grandes vitesses de commutation.

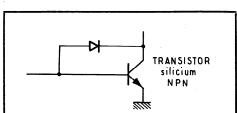

Le premier de ces concepts a pour nom « Baker Clamp », terme que l'on pourrait traduire par limiteur Baker. Il consiste à insérer une diode au germanium entre base et collecteur d'un transistor NPN.

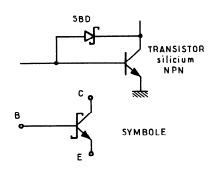

Le deuxième concept réside dans la réalisation même de la diode de Clamping (ou de limitation), laquelle a conduit à la mise au point de la SBD (Schottky Barrier Diode) que l'on trouve aujourd'hui dans les circuits intégrés ALS et AS.

### Principe du limiteur Baker

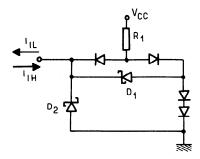

On l'a vu, un moyen d'éviter la sursaturation d'un transistor consiste à utiliser la diode de limitation Baker ainsi que le montre la figure 1. Il s'agit d'une diode dans laquelle la tension directe est de 0,3 à 0,4 V, comparée à la tension de 0,7 V de jonction base-émetteur.

Quand un courant est appliqué sur sa base, celui-ci tend à amener le transistor à saturation, voire à sursaturation. La tension collecteur diminue alors jusqu'à rendre la diode au germanium conductrice, dérivant ainsi l'excès de courant de base. Le transistor est donc maintenu en dehors de la zone de sur-saturation. La base ne stocke plus de charges excessives, et le temps de commutation se trouve considérablement réduit.

Toutefois, comme on ne saurait intégrer une diode au germanium dans un circuit monolithique au silicium, la voie suivie pour obtenir un circuit intégré consiste à remplacer cette diode au germanium par une diode au silicium présentant une tension directe plus basse que la jonction base-émetteur du transistor. Les diodes PN normales ne répondant pas à cette caractéristique, la diode SBD a été mise au point remplir cette fonction (fig. 2).

Fig. 1. – Limiteur baker (« baker clamp »).

Fig. 2. – Transistor avec limiteur baker SBD.

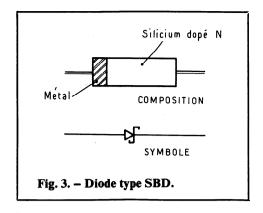

# La diode SBD « Schottky Barrier Diode »

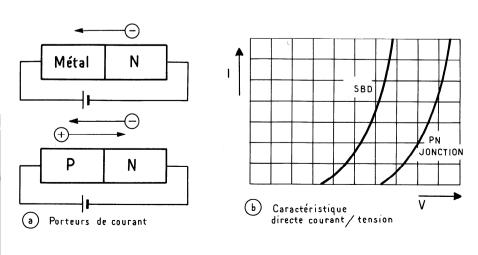

La diode SBD est une jonction métal semiconducteur, ce dernier étant dopé N (fig. 3). On sait, en effet, que dans un métal, les bandes de valence et de conduction se recouvrent, rendant possible l'existence d'un grand nombre de niveaux d'énergie libres, susceptibles d'être occupés par des électrons injectés dans la bande de conduction. Par ailleurs, dans un semiconducteur, il existe un nombre fini d'électrons dans la bande de conduction, déterminé principalement par le niveau de l'énergie thermique et le nombre d'atomes d'impuretés contenues dans le matériau lui-même.

Lorsqu'une jonction métal-semiconducteur est réalisée, les électrons libres issus de la bande de conduction du semiconducteur vont occuper les niveaux d'énergie libres du métal.

Bien évidemment, cette migration d'électrons génère une tension d'apauvrissement au niveau de la jonction, qui s'oppose à leur déplacement et peut s'avérer suffisante au maintien d'une situation d'équilibre où il n'y a pas de réel déplacement au travers de cette même jonction.

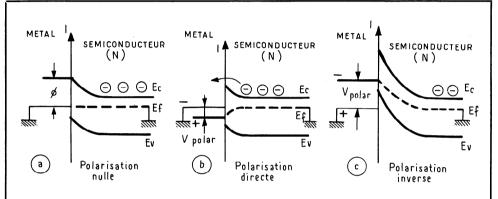

Sous une polarisation directe (tension positive sur le métal), une certaine quantité d'électrons accumulés sur cette jonction bénéficiera d'une énergie suffisante pour traverser la barrière de potentiel et pénétrer ainsi dans la partie métallique. Il s'agit là du phénomène dit « d'injection thermique », encore appelé « hot injection ». Lorsque la tension directe (VD) appliquée à la jonction augmente, la largeur de la barrière diminue et le courant direct augmente à son tour.

Quand la SBD est polarisée en inverse, les électrons du semiconducteur demandent une énergie bien plus importante pour franchir la bar-

rière. Les électrons du métal voient de leur côté une barrière de potentiel pratiquement indépendante de la tension de polarisation, et le courant inverse reste donc très faible, et n'augmentera pas de manière significative jusqu'au moment où le claquage en avalanche survient (fig. 4). Ainsi s'explique la propriété de redressement de la diode SBD.

Toutefois, on observe qu'au niveau de la sortie du transistor, qui met également en jeu une jonction métal-semiconducteur dopé N, on ne retrouve plus cette caractéristique mais au contraire un contact ohmi-

que. L'explication tient ici dans les niveaux de dopage différents du semiconducteur.

En effet, plus le niveau de dopage augmente, plus le contact devient ohmique (fig. 5).

Au phénomène de redressement décrit plut haut s'ajoute une caractéristique importante : la vitesse de commutation. On sait que dans une SBD, le courant est dû aux porteurs majoritaires, alors que dans une jonction PN, il est dû aux porteurs minoritaires. Or, le stockage de porteurs minoritaires limite le temps de

Fig. 4. -

Fig. 5. - Caractéristique courant/tension d'une diode type SBD.

Fig. 6. - Différence entre diodes PN et SBD.

communtation d'une jonction PN au moment du passage de polarisation directe à polarisation inverse.

Ceci explique qu'une diode SBD soit plus rapide qu'une jonction PN, même quand cette dernière est dopée à l'or.

Une autre différence majeure intéresse la tension directe (fig. 6). Pour des diodes de même surface, la SBD, indépendamment du métal utilisé, présente un courant direct plus important à tension directe identique. Il en résulte que, pour un courant donné, la tension directe d'une SBD est inférieure à celle d'une jonction PN.

La SBD remplit donc la fonction d'une diode rapide au silicium capable de limiter la saturation d'un transistor NPN, lui-même au silicium (fig. 6).

#### Processus de fabrication

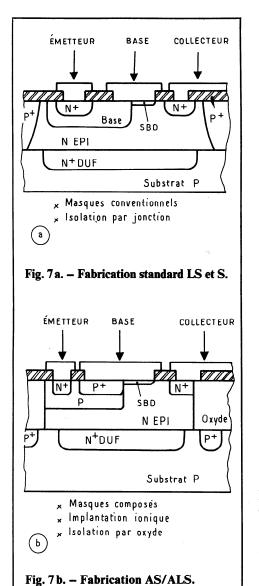

L'Advanced Low Power Schottky diffère de la Low Power Schottky

classique au niveau de la fabrication en ce sens où elle utilise l'implantation ionique d'impuretés au lieu de la diffusion. Il en résulte un meilleur contrôle de la profondeur du dopage et de la résolution de géométrie. De plus, une très fine couche épitaxiale et de petites géométrie réduisent sensiblement les capacités parasites. la performance du produit est aussi améliorée par l'utilisation d'oxyde pour isoler les transistors au lieu de l'isolation par diffusion, ce qui a également pour effet de réduire la capacité collecteursubstrat (fig. 6 et 7).

# Caractéristiques de la technologie

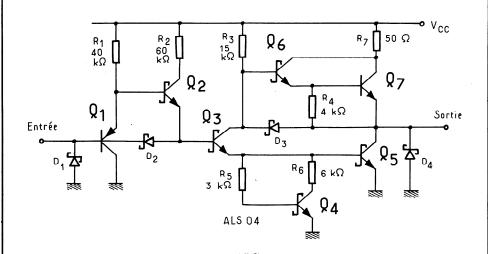

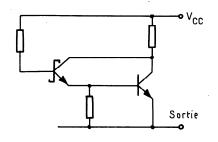

# Analyse d'un inverseur de la série 54 ALS/74 ALS

L'inverseur de la série 54 ALS/74 ALS (fig. 8) associe les caractéristiques d'un circuit TTL amélioré par les avantages technologiques, des diodes de « clamp » schottky, de l'implantation ionique, et de l'isolation par oxyde, pour atteindre un temps de commutation très court tout en conservant un faible facteur vitesse-consommation (facteur de mérite 4 pj).

Plus précisément les améliorations et les avantages de la technologie sont les suivants :

a) la limitation par diode schottky de tous les transistors saturés élimine les charges excessives stockées sur les bases, ce qui améliore d'une manière significative le temps de blocage des transistors;

- b) cette élimination du temps de stockage des transistors permet aussi d'obtenir des temps de commutation très stables sur toute la gamme de température;

- c) un circuit de blocage actif a été inséré pour améliorer la caractéristique de transfert et augmenter l'immunité au bruit en régime dynamique :

- d) une diode schottky de protection est prévue aux entrées pour éliminer l'effet d'une tension négative. Sa faible tension directe et son temps de recouvrement rapide permettent d'obtenir une meilleure protection par rapport à une diode conventionnelle à jonction P/N;

- e) le procédéd'implantation ionique permet, quant à lui, d'utiliser de faibles géométries diminuant les capacités parasites, et améliorant les temps de commutation :

- f) la réduction de la capacité épisubstrat par l'utilisation de l'isolation par oxyde contribue également à diminuer les temps de commutation

L'analyse de la caractéristique d'entrée/sortie d'une porte ALS permet d'appréhender le fonctionnement du circuit dans la plupart des applications.

Fig. 8. – Schéma d'une porte inverseuse ALS.

|         |                      |                      |                       | ·                     |

|---------|----------------------|----------------------|-----------------------|-----------------------|

| TA      | "AS" V <sub>OH</sub> | "AS" V <sub>OL</sub> | "ALS" V <sub>OH</sub> | "ALS" V <sub>OL</sub> |

| — 55 °C | 3,4                  | 0,26                 | 3,3                   | 0,26                  |

| 25 ∘C   | 3,5                  | 0,24                 | 3,4                   | 0,24                  |

| 125 °C  | 4,0                  | 0,25                 | 3,9                   | 0,25                  |

Fig. 9. - Tensions de sortie typiques en fonction de la température.

Fig. 10. - Courbe de transfert à température ambiante.

Fig. 11. – Circuit équivalent d'entrée d'une porte ALS.

Fig. 12. – Série 54 ALS/74 ALS. Schéma de sortie équivalent du niveau logique haut.

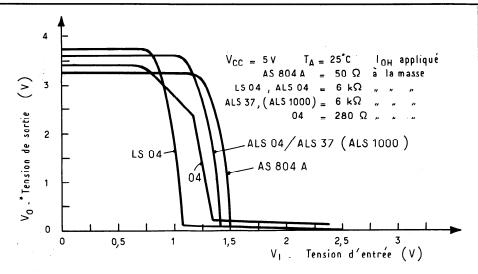

La fig. 10 montre ces caractéristiques comparées à celle de portes de série N et LS.

Il est possible d'observer que le coude de la caractéristique AS et ALS est bien mieux défini au niveau du seuil d'entrée.

L'amélioration du niveau de sortie est due au circuit de blocage actif (plutôt que passif) du transistor ( $Q_5$ ). De plus la chute de tension de la diode dans une sortie standard est remplacée ici par un  $V_{BE}$  de transistor traversé par un faible courant. Ceci procure une meilleure immunité au bruit pour l'ALS comparée à la TTL, et la LS.

### Test des paramètres d'entrée

Le schéma équivalent d'une entrée de porte ALS en régime statique, est donné par la fig. 11.

Le courant d'entrée au niveau logique bas  $(I_{IL})$  est principalement déterminé par  $R_1$ ; néanmoins ce courant  $I_{IL}$  est aussi fonction de la tension d'alimentation  $V_{CC}$ , de la température ambiante  $T_A$  et de la tension d'entrée  $V_{IL}$ . Pendant le test, à l'exception de l'entrée testée toutes les autres entrées sont maintenues au niveau logique haut.

Test de la diode de protection D<sub>2</sub> Ce test consiste à vérifier que la chute de tension aux bornes de D<sub>2</sub> ne dépasse pas 1,2 V pour un courant direct de 18 mA.

Ces valeurs sont garanties V<sub>CC min</sub> sur toute la gamme de température.

Seuil de commutation en entrée II est assuré par  $Q_1$ ,  $Q_2$ ,  $Q_3$  et  $Q_5$  associés dans la relation suivante :

$V_{\text{seuil}} = V_{\text{BE } 02} + V_{\text{BE } 03} + V_{\text{BE } 05} - V_{\text{BE } 01}$

ce qui donne une valeur approximative de 1,3 V.

Le principe utilisé est similaire à celui utilisé en technologie LS à ceci près que le courant  $I_{IL}$  nécessaire, a été diminué de moitié par l'introduction de  $Q_2$ . Le niveau de sortie haut  $V_{OH}$  est supérieur dans la technologie ALS du fait du circuit de blocage actif  $Q_4$ :

$$\begin{array}{l} V_{OH} \, = \, V_{CC} \, - \, (I_{b \, (\Omega_{\hat{b})}} \, R_3 \, + \, V_{BE \, \Omega \hat{b}} \, + \\ V_{BE \, \Omega_7}). \end{array}$$

La sortance est de 10 pour la série 54 ALS et de 20 pour la série 74 ALS avec un  $I_{\rm OL}$  garanti de 4 mA.

L'amélioration du produit vitesseconsommation des séries 54 ALS/74 ALS dans un rapport 5 comparé aux séries 54 LS/74 LS est due essentiellement aux précautions prises dans l'élaboration du fonctionnement statique et dynamique du circuit.

Paramètres du circuit

Les tests des circuits effectués aux extrêmes de la spécification procurent une marge de sécurité appréciable.

Tous les paramètres statiques (DC) de la spécification sont garantis sur toute la gamme de température (-55 à +125 °C pour la série 54 ALS et de 0 à 70 °C pour la série 74 ALS) et sur toute la plage de tension d'alimentation, 4,5 à 5,5 V.

Caractéristique de transfert

Le tableau de la figure 9 donne les valeurs typiques des V<sub>OH</sub> et V<sub>OL</sub> en fonction de la température pour les technologies ALS et AS.

A noter que ces valeurs ne varient pratiquement pas sur toute la gamme de température et dans des conditions normales d'utilisation étant entendu que le V<sub>OH</sub> est directement lié à la tension d'alimentation utilisée

Courant d'entrée au niveau logique haut (liu)

Ce test est réalisé à V<sub>CC max.</sub> avec toutes les entrées non utilisées à la masse. Le but de ce test étant de rejeter des pièces risquant de dégrader le V<sub>OH</sub> du circuit les précédant dans le cas d'utilisation à sortance maximale.

Associé à ce test de I<sub>IH</sub> un test de tension de claquage est également réalisé sous V<sub>CC max</sub>. Il est important car la jonction base émetteur de faible dimension peut facilement être mise en « sur dissipation ».

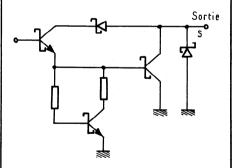

### Test des paramètres de sortie

La sortie la plus courante en TTL est de type « push pull » « totem pole », qui permet d'obtenir une faible impédance de sortie au niveau logique haut et au niveau bas. Les deux familles ALS et AS utilisent cette configuration avec des sortances respectives de 20 et 10 à la fois pour les niveaux haut et bas (voir tableau 2).

Courant de sortie au niveau logique haut l<sub>OH</sub>

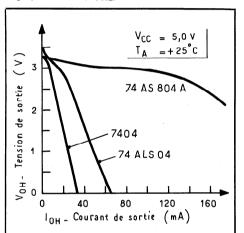

La capacité pour une sortie totem pole à pouvoir délivrer un courant au niveau logique haut se teste en forçant un I<sub>OH</sub> pendant la mesure du V<sub>OH</sub>.

Néanmoins la qualité de l'étage de sortie est mieux évaluée par la mesure du courant de court-circuit à la masse (los).

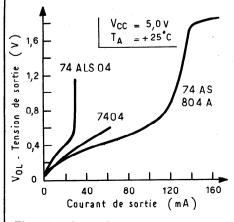

La figure 12 montre le circuit équivalent de sortie au niveau logique haut et la figure 13 les courbes de V<sub>OH</sub> relevées pour les circuits 7404, 74ALS04 et 74AS804A. Ce test se fait à V<sub>CC min</sub>, une entrée étant connectée au niveau logique bas (valeur limite la plus défavorable), les autres au V<sub>CC</sub>.

Courant de sortie au niveau logique bas l<sub>ol</sub>

La figure 14 montre le circuit équivalent de sortie au niveau logique bas et la figure 15 les courbes de  $V_{\rm OL}$  relevées. Ce test est également réalisé à  $V_{\rm CC\,min}$ .

#### Vitesse de commutation

Deux paramètres de commutation sont garantis dans les séries AS et ALS; le temps de propagation d'un niveau logique haut vers un niveau logique bas (T<sub>PHL</sub>) et d'une manière

Fig. 13. – Caractéristique de sortie au niveau logique haut.

Fig. 14. – Schéma de forme équivalant au niveau logique bas.

Fig. 15. – Caractéristique de sortie au niveau logique bas.

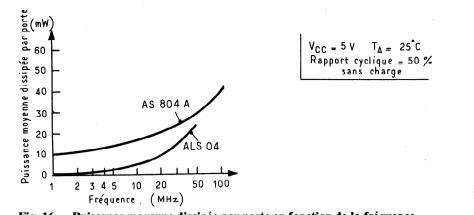

Fig. 16. - Puissance moyenne dissipée par porte en fonction de la fréquence.

| Paramètres<br>(volts)                    | AS<br>(0 °C à 70 °C) | ALS<br>(0 °C à 70 °C) | AS<br>(-55 °C à 125 °C) | ALS<br>(-55 °C à 125 °C) |  |  |

|------------------------------------------|----------------------|-----------------------|-------------------------|--------------------------|--|--|

| VIH (MIN)                                | 2                    | 2                     | 2                       | 2                        |  |  |

| VIL (MAX)                                | 0,8                  | 0,8                   | 0,8                     | 0,8                      |  |  |

| VOH (MIN)                                | 2,7                  | 2,7                   | 2,5                     | 2,5                      |  |  |

| VOL (MAX)                                | 0,5                  | 0,5                   | 0,5                     | 0,4                      |  |  |

| Marge de bruit au<br>niveau logique haut | 0,7                  | 0,7                   | 0,5                     | 0,5                      |  |  |

| Marge de bruit au<br>niveau logique bas  | 0,3                  | 0,3                   | 0,3                     | 0,4                      |  |  |

Fig. 18. - Paramètres de sortie (conditions externes).

similaire le temps de propagation du niveau logique bas vers un niveau logique haut (T<sub>PLH</sub>). Ces deux paramètres sont spécifiés en typique sous les conditions :

$$V_{CC}=5\,V,\,T_A=25\,\circ C,\,C_L=15\,pF,\,R_L=500\,\Omega$$

et en min et max sous les conditions  $V_{CC}=4.5\,V$ ,  $5.5\,V$ ,  $T_A=0\,\circ\,70\,\circ C$ , (74ALS~74AS),  $C_L=50\,pF$ ,  $R_L=500\,\Omega$

$$T_A = -55 \, ^{\circ}\text{C} + 125 \, ^{\circ}\text{C} \, (54 \text{ ALS } 54 \text{ AS}), \, C_L = 50 \, \text{pF}, \, R_L = 500 \, \Omega.$$

La figure 16 montre la variation du temps de propagation moyen en fonction d'une charge capacitive.

Il est à noter que ces temps de propagation ne varient pratiquement pas avec la température.

La figure 16 montre la puissance dissipée moyenne en fonction de la fréquence de fonctionnement.

Marge de bruit en régime statique Sans vouloir entrer dans le détail, il est rappelé que la marge de bruit est la spécification d'une tension qui garantit l'immunité au bruit en régime statique. Cette marge de bruit est définie comme étant la différence entre le niveau logique garanti d'une entrée (V<sub>IH min</sub> ou V<sub>IL max</sub>) et le niveau logique garanti d'une sortie (V<sub>OH min</sub> ou V<sub>OL max</sub>) permettant de commander une telle entrée.

Le tableau de la figure 17 donne la valeur de tous ces paramètres pour l'AS et l'ALS.

Ces quelques lignes n'ont eu pour but que de mettre en relief les principaux paramètres favorisés par la nouvelle technologie des circuits AS et ALS et il convient d'approfondir les spécifications de chacun d'eux pour utiliser pleinement les possibilités qu'ils offrent.

Afin de permettre aux lecteurs l'utilisation rationnelle de l'ensemble des familles TTL,

le tableau 1 indique les courants d'entrée,

le tableau 2 indique les sortances.

Ces tableaux peuvent être utilisés dans deux cas :

- soit pour le remplacement d'une fonction LS par une fonction ALS ou autre;

- soit lors d'une étude nouvelle, utilisant plusieurs familles TTL, pour optimiser les performances.

### **Perspectives**

Ces deux familles s'attaquent à des objectifs différents.

L'ALS remplacera à terme la LS, d'ailleurs les premières 150 fonc-

# Technique appliquée

# Dans Toute l'Electronique

## En novembre:

## Thèmes principaux

- L'optoélectronique

- Télécommunication et Radionavigation

### Produits du mois

■ Les composants optoélectronique

# En décembre :

## Thèmes principaux

- Mesure sur le secteur 50 Hz

- Instrumentation de laboratoire et le supplément spécial Salon Mesucora Elec.

### Produits du mois

■ Les nouveautés du Salon

# En janvier:

## Thème principal

■ Les hyperfréquences

### Produits du mois

■ Les composants hyperfréquence

| Séries              | Niveau<br>d'entrée | Courant<br>d'entrée | Tableau 1 : courants d'entrée normalisés |                     |                     |                           |                     |                           |                             |  |

|---------------------|--------------------|---------------------|------------------------------------------|---------------------|---------------------|---------------------------|---------------------|---------------------------|-----------------------------|--|

|                     |                    |                     | Séries<br>54/74                          | Séries<br>54 H/74 H | Séries<br>54 L/74 L | Séries<br>54 LS<br>/74 LS | Séries<br>54 S/74 S | Séries<br>54 AS<br>/74 AS | Séries<br>54 ALS<br>/74 ALS |  |

| 54/74               | Н                  | 40μΑ                | 1                                        | 0,8                 | 4                   | 2                         | 0,8                 | 0,2                       | 2                           |  |

|                     | L                  | 1,6mA               | 1                                        | 0,8                 | 9                   | 4,5                       | 0,8                 | 0,8                       | 8                           |  |

| 54 H/74 H           | Н                  | 50μΑ                | 1,25                                     | 1                   | 5                   | 2,5                       | 1                   | 0,25                      | 2,5                         |  |

|                     | L                  | 2mA                 | 1,25                                     | 1                   | 11                  | 5,5                       | 1                   | 1                         | 10                          |  |

| <b>54</b> L/74 L    | Н                  | 10μΑ                | 0,25                                     | 0,2                 | 1                   | 0,5                       | 0,2                 | 0,05                      | 0,5                         |  |

|                     | · L                | 0,18mA              | 0,11                                     | 0,09                | 1                   | 0,5                       | 0,09                | 0,09                      | 0,9                         |  |

| <b>54 LS</b> /74 LS | . н                | 20μΑ                | 0,5                                      | 0,4                 | 2                   | 1                         | 0,4                 | 0,1                       | 1                           |  |

| 54 LS               | L                  | 0,36mA              | 0,225                                    | 0,18                | 2                   | 1                         | 0,18                | 0,18                      | 1,8                         |  |

| 74 LS               | L                  | 0,36mA              | 0,225                                    | 0,18                | 2                   | 1                         | 0,18                | 0,18                      | 1,8                         |  |

| 54 S/74 S           | Н                  | 50μΑ                | 1,25                                     | 1                   | 5                   | 2,5                       | 1                   | 0,25                      | 2,5                         |  |

|                     | L                  | 2mA                 | 1,25                                     | 1                   | 11                  | 5,5                       | 1                   | 1                         | 10                          |  |

| 54 AS/74 AS         | Н                  | 200μΑ               | 5                                        | 4                   | 20                  | 10                        | 4                   | 1                         | 10                          |  |

|                     | L                  | 2mA                 | 1,25                                     | 1                   | 11                  | 5 ·                       | 1                   | 1                         | 10                          |  |

| 45 ALS/74 ALS       | Н                  | 20μΑ                | 0,5                                      | 0,4                 | . 2                 | 1                         | 0,4                 | 0,1                       | 1                           |  |

|                     | L                  | 0,2mA               | 0,125                                    | 0,1                 | 1,1                 | 0,5                       | 0,1                 | 0,1                       | 1                           |  |

|               | Niveau<br>de<br>sortie | Courant<br>de<br>sortie | Tableau 2 : sortance |                     |                     |                           |                     |                           |                             |  |

|---------------|------------------------|-------------------------|----------------------|---------------------|---------------------|---------------------------|---------------------|---------------------------|-----------------------------|--|

| Séries        |                        |                         | Séries<br>54/74      | Séries<br>54 H/74 H | Séries<br>54 L/74 L | Séries<br>54 LS<br>/74 LS | Séries<br>54 S/74 S | Séries<br>54 AS<br>/74 AS | Séries<br>54 ALS<br>/74 ALS |  |

| 54/74         | Н                      | 400μΑ<br>/800μΑ         | 10/20                | 8/16                | 40/80               | 20/40                     | 8/16                | 2/4                       | 20/40                       |  |

|               | L                      | 16mA                    | . 10                 | 8                   | 89                  | 44                        | 8                   | 8                         | 80                          |  |

| 54H/74H       | Н                      | 500μΑ                   | 12,5                 | 10                  | 50                  | 25                        | 10                  | 2,5                       | 25                          |  |

|               | L                      | 20mA                    | 12,5                 | 10                  | 111                 | 55                        | 10                  | 10                        | 100                         |  |

| 741 /741      | Н                      | 100μΑ                   | 2,5                  | 2                   | 10                  | 5                         | 2                   | 0,5                       | 5                           |  |

| 74L/74L       | L                      | 2mA                     | 1,25                 | 1                   | 11                  | 5,5                       | 1                   | 1                         | 10                          |  |

| 54 LS/74 LS   | Н                      | 40μΑ                    | 10                   | 8                   | 40                  | 20                        | 8                   | 2                         | 20                          |  |

| 54 LS         | L                      | 5mA                     | 2,5                  | 2                   | 22                  | 11                        | 2,5                 | 2,5                       | 25                          |  |

| 74 LS         | L                      | 8mA                     | 5                    | 4                   | 44                  | 22                        | 4                   | 4                         | 40                          |  |

| 54 S/74 S     | Н                      | 1mA                     | 25                   | 20                  | 100                 | 50                        | 20                  | 5                         | 50                          |  |

|               | L                      | 20mA                    | 12,5                 | 10                  | 111                 | 50                        | 10                  | 10                        | 100                         |  |

| 54 AS/74 AS   | Н                      | 2mA                     | 50                   | 40                  | 200                 | 100                       | 40                  | 10                        | 100                         |  |

|               | L                      | 20mA                    | 12,5                 | 10                  | 111                 | 50                        | 10                  | 10                        | 100                         |  |

| 54 ALS/74 ALS | Н                      | 0,4mA                   | 10                   | 8                   | 40                  | 20                        | 8                   | 2                         | 20                          |  |

|               | L                      | 4mA                     | 2,5                  | 2                   | 5                   | 10                        | 2                   | 2                         | 20                          |  |

tions disponibles chez Texas Instruments ne sont-elles pas compatibles broche à broche avec la LS.

Cette compatibilité permet une introduction rapide de l'ALS sur des plaques déjà équipées en LS, sans étude nouvelle, donc à moindres frais. C'est ce qui dès à présent fait le succès de cette famille dont six secondes sources sont dès à présent connues.

L'utilisation de l'AS avec ces 1,5 ns par porte, nécessitera quant à elle, de par sa vitesse, la mise en étude de nouveaux systèmes rapides. Son introduction sera plus lente. La gamme de produits proposée par *Texas* et *National* sera de l'ordre de 70 fonctions.

Notons à cet effet que c'est la première fois que *Texas* et *National* signent un accord de seconde source sur des produits nouveaux.

La technologie et le processus de fabrication utilisés nous permettent d'envisager à moyen terme, des améliorations significatives des performances.

Le procédé lithographique employé autorise une définition de  $4\,\mu$ , valeur devant être ramenée à  $2\,\mu$  à brève échéance, permettant tout à la fois d'augmenter la vitesse, de réduire la puissance consommée, et de franchir grâce aux avantages ainsi conjugués un nouveau pas dans l'échelle de complexité.