# **SOLAR**

SCM64 - SC512

Mémoires 64 et 512 KMots

FONDS DOCUMENTAIRE SMP

MANUEL D'UTILISATION

MEMOIRES 32 A 512 K

Gamme : SOLAR

**Systèmes**: 16/40,16/65,16/75,16/85

Objet : Ce manuel décrit l'utilisation des mémoires

SOLAR de 32K à 512K réalisées avec la carte

1 150 263 (32 à 128K) et la carte

1 150 266 (128K à 512K)

Date d'édition : MAI 1982

## AVERTISSEMENT

Mémoires 32K à 128K (carte 1 150 263) : chapitres 1 à 3

Mémoires 128K à 512K (carte 1 150 266) : chapitres 4 à 6

## - TABLE DES MATIERES -

| <u> </u> | PRESENTATION. MÉMOIRES 32 A 128K                          | . 1 |

|----------|-----------------------------------------------------------|-----|

|          | 1.1 BUT                                                   | . 1 |

|          | 1.2 CONSTITUTION DES MODULES                              | . 1 |

|          | 1.3 CONTRAINTES DE CONFIGURATION                          | . 1 |

|          | 1.4 CONTRAINTES D'UTILISATION                             | . 2 |

|          | 1.4.1 Environnement                                       | . 2 |

|          | 1.4.2 Caractéristiques électriques                        | . 2 |

|          | 1.5 PERFORMANCES                                          | . 2 |

|          | 1.6 OPTION                                                | . 3 |

| 2        | FONCTIONNEMENT DU MODULE MÉMOIRE 32 K A 128 K             | . 1 |

|          | 2.1 GENERALITES                                           | . 1 |

|          | 2.2 PRINCIPE DE FONCTIONNEMENT                            | . 1 |

|          | 2.3 SAUVEGARDE MÉMOIRE                                    | . 3 |

| 3        | MISE EN OEUVRE (MÉMOIRES 32 A 128 K)                      | . 1 |

|          | 3.1 ADRESSAGE                                             | . 1 |

|          | 3.2 CIRCUIT DE "TASSEMENT"                                | . 2 |

|          | 3.3 MODE NORMAL SANS INTERLIVING                          | . 2 |

|          | 3.4 "INTERLIVING"                                         | . 2 |

|          | 3.4.1 "Interliving" d'ordre 2                             | . 3 |

|          | 3.4.2 "Interliving" d'ordre 4                             | . 3 |

|          | 3.5 RÉGLAGE DU DESKEWING                                  | . 3 |

|          | 3.6 INSTALLATION ET RACCORDEMENT                          | . 8 |

|          | 3.7 MOYEN DE TEST                                         | .9  |

| 4        | PRESENTATION (MÉMOIRES 128K A 512K)4                      | . 1 |

|          | 4.1 BUT                                                   | . 1 |

|          | 4.2 CONSTITUTION DES MODULES                              | . 1 |

|          | 4.3 CONTRAINTES DE CONFIGURATION                          | . 1 |

|          | 4.4 CONTRAINTES D'UTILISATION                             | . 2 |

|          | 4.4.1 Environnement                                       | . 2 |

|          | 4.4.2 Caractéristiques électriques4                       | . 2 |

|          | 4.5 PERFORMANCES                                          | . 3 |

|          | 4.6 OPTION                                                | . 4 |

| 5        | FONCTIONNEMENT DU MODULE MÉMOIRE (MÉMOIRES 128 K A 512 K) | . 1 |

|      |        | ). т | GENERALITES                                                          |

|------|--------|------|----------------------------------------------------------------------|

| Bull | 9      | 5.2  | PRINCIPE DE FONCTIONNEMENT                                           |

|      | 5      | 5.3  | SAUVEGARDE MÉMOIRE                                                   |

|      | 6 MISE | E EN | OEUVRE. POSITION DES CAVALIERS SUR EMBASES (MÉMOIRES 128K A 512K)6.1 |

|      | 6      | 5.1  | CAPACITÉ DE LA CARTE (TB 011)                                        |

|      | 6      | 5.2  | AFFECTATION A UN NUMÉRO DE PROCESSEUR (TB 007 . TB 008)6.2           |

|      | 6      | 5.3  | ZONE D'ADRESSAGE MODE NORMAL                                         |

|      |        |      | 6.3.1 Mode normal pour toutes VU                                     |

|      |        |      | 6.3.2 Mode normal. zone d'adressage                                  |

|      | 6      | 5.4  | ZONE D'ADRESSAGE MODE INTERLIVING D'ORDRE 2                          |

|      |        |      | 6.4.1 Interliving avec 2 cartes 1.150.266.03 (128 K)6.5              |

|      |        |      | 6.4.2 Interliving avec 2 cartes 1 150 266 02 (256 K)6.6              |

|      |        |      | 6.4.3 Interliving avec 2 cartes 1 150 266 01 (512 K)6.7              |

|      | 6      | 5.5  | RÉGLAGE DU DESKEWING                                                 |

|      | 6      | 5.6  | INSTALLATION ET RACCORDEMENT                                         |

6.7 MOYEN DE TEST ......6.9

## 1 PRESENTATION - MEMOIRES 32 A 128K =

### 1.1 BUT

La mémoire vive à semi-conducteurs est destinée à stocker les informations "Instructions" ou "opérande" relatives à un ou plusieurs processeurs des Types SOLAR 16-40 ou 16-75 ou IDP.

Les mots stockés ont une longueur de 17 bits (16 bits d'information et 1 bit de parité). Le bit de parité est élaboré et contrôlé par le processeur.

#### 1.2 CONSTITUTION DES MODULES.

Ces mémoires dites "32 K à 128 K" se répartissent en 3 modules

| CAPACITE | N° DU MODULE | CONSTITUTION                 |                                       |

|----------|--------------|------------------------------|---------------------------------------|

| 128 К    | 1 159 234 01 | 1 150 263 01<br>1 153 064 04 | Carte Mémoire 128 K<br>Cable batterie |

| 64 K     | 1 159 234 03 | 1 150 263 03<br>1 153 064 04 | Carte Mémoire 64 K<br>Cable batterie  |

| 32 K     | 1 159 234 04 | 1 150 263 04<br>1 153 064 04 | Carte Mémoire 32 K<br>Cable batterie  |

#### 1.3 CONTRAINTES DE CONFIGURATION.

La carte est enfichable dans les bacs de hauteur :

12 U = Cartes verticales

6 U = Cartes horizontales

4 U = Cartes horizontales.

### 1.4.1 Environnement

- Température 0°C <= T <= 40°C

- Humidité : <= 90 % sans condensation

- Chocs et vibrations : compatible avec les équipements électroniques standard.

Des précautions doivent être prises lors des manipulations des cartes notamment pour les pots en ferrite des alimentations.

## 1.4.2 Caractéristiques électriques

Consommation sur tension bac.

AU REPOS A CADENCE MAX

5V 2A 2A

24V 0,4A 0.5A

Consommation sur batterie de sauvegarde

16V 0.5A

#### 1.5 PERFORMANCES

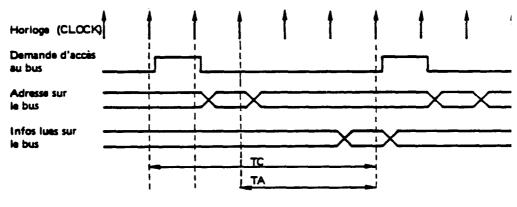

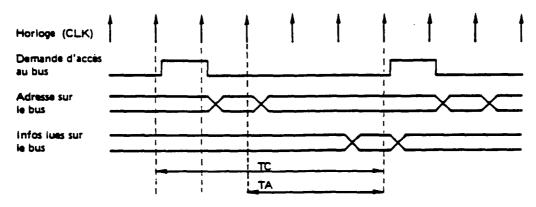

Utilisation en mono processeur :

Figure 1

TC = Temps de cycle = 5 CLOCK (lecture écriture ou échange)

TA = Temps d'accès = 3 CLOCK (lecture ou échange)

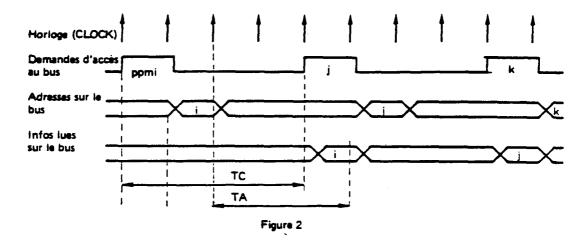

Utilisation en multi-processeur

TC = 4 CLOCK (lecture. écriture ou échange)

TA = 3 CLOCK (lecture ou échange)

## Remarque importante :

Les boitiers mémoires MOS utilisés sur le module sont du type dynamique, de ce fait, il est nécessaire de rafraîchir l'information contenue en mémoire. Une horloge interne déclenche toutes les 14us un cycle de rafraîchissement qui dure 3 CLOCK. Si un processeur demande à ce moment un accès à la mémoire, cet accès est retardé jusqu'à la fin du rafraîchissement en cours. Ce qui allonge d'autant la durée de l'accès et du cycle demandé. Théoriquement, la mémoire étant occupée 2 % de son temps à faire des rafraîchissements, il convient d'ajouter 2 % à la durée moyenne d'un accès. Pratiquement, à cause d'une resynchronisation partielle des demandes de cycle simultanées, cette augmentation de durée peut être estimée à 1 % , donc d'une influence négligeable sur les performances du système.

## 1.6 OPTION

Pour assurer la sauvegarde de l'information contenue en mémoire, en cas de coupure des alimentations du bac, le module peut être équipé de batteries.

Module 0,5 AH

Ou Module 1,2 AH N° 1 159 111 01

ou Module 7 AH N° 1 159 111 03

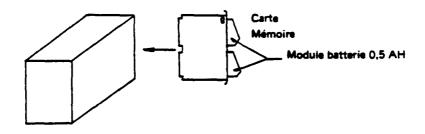

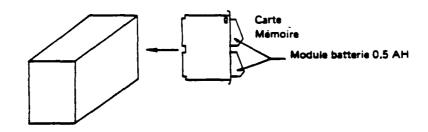

Le module 0,5 AH est enfiché directement sur les connecteurs avant de la carte mémoire.

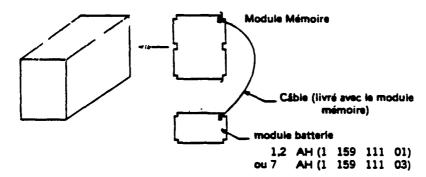

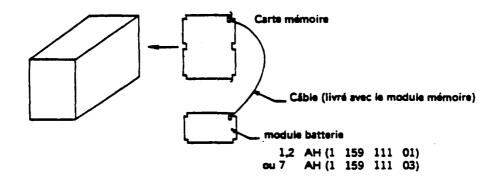

Les modules = 1,2 AH, ou 7 AH sont placés dans le bac et sont raccordés sur un bornier situé à l'avant de la carte mémoire par un câble.

## 2 FONCTIONNEMENT DU MODULE MEMOIRE

### 32 K A 128 K

#### 2.1 GENERALITES

Le module mémoire dialogue avec le ou les processeurs auxquels il est affecté par l'intermédiaire du bus mémoire (Voir Notice N° 1 160 902 00).

La mémoire est constituée à base de boîtiers RAM(16K dynamiques 16 broches de temps d'accès à la lecture 200 ns).

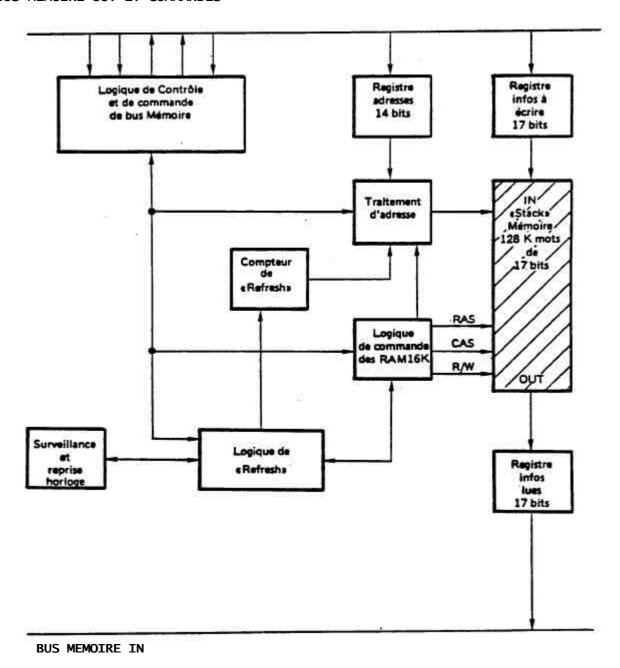

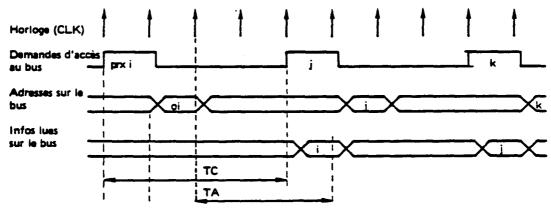

Un synoptique du module est représenté sur la figure 3.

Le module peut effectuer trois types de cycles Lecture, Ecriture et Echange.

#### 2.2 PRINCIPE DE FONCTIONNEMENT

On peut diviser le module en deux parties Principales

- A) Circuits de dialogue avec le bus I/0

- L'interface de contrôle = elle assure le dialogue avec le bus mémoire (si mémoire occupée : gestion de la file d'attente, rappel du processeur en attente, etc ... ), le chargement des registres "adresse" et "information à écrire", le lancement d'un cycle mémoire à la base de temps et l'émission des infos lues sur le bus mémoire lorsque la base de temps lui indique que le cycle est terminé.

- 2) Les différents registres du module : adresse, information à écrire, information lue

- 3) Les drivers et récepteurs de bus (ne sont pas représentés sur le synoptique).

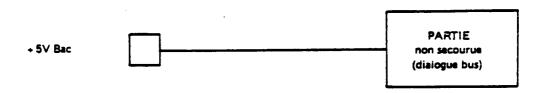

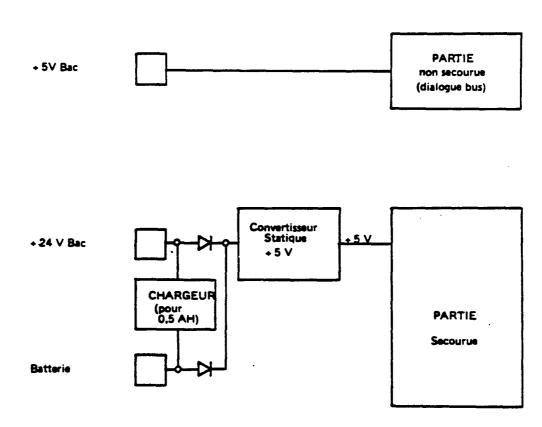

Toute cette partie synchrone est alimentée directement à partir des tensions du bac, car son fonctionnement est inutile à la sauvegarde des informations stockées.

- B) Une partie "mémoire" comprenant :

- b-1) Le stock mémoire avec ses circuits de dédocage et drivers associés (non représentés).

- B-2) La logique de rafraîchissement, le compteur de rafraîchissement, la surveillance d'horloge et le multiplexeur d'adresses. Ces circuits assurent les séquences et les commandes nécessaires au bon fonctionnement du stock mémoire.

Ces circuits sont alimentés par des alimentations secourues situées sur la

carte et fonctionnent suivant l'état du système d'alimentation soit à partir du  $+\ 24\ V$  bac, soit de la tension batterie (Option) la commutation étant entièrement automatique.

## BUS MEMOIRE OUT ET COMMANDES

Figure 3

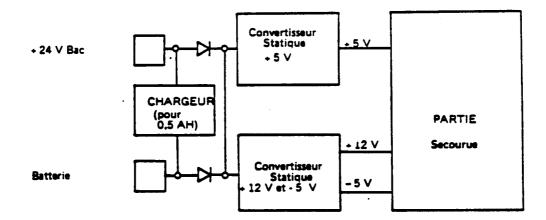

### 2.3 SAUVEGARDE MEMOIRE

La sauvegarde de l'information est assurée, en option, par un système de batteries Cadmium - Nickel de capacité 0,5 à 7 AH. Pour les temps de sauvegarde se rapporter au manuel d'utilisation des "batteries". 1 159 110 ID 30.

Un synoptique du système d'alimentation est représenté sur la figure 4.

Un voyant implanté sur l'avant des cartes mémoire permet de vérifier la tension de la batterie. Il s'éteint lorsque la tension aux bornes de la batterie tombe en dessous de 15 volts'.

Figure 4

## 3 MISE EN ŒUVRE (MEMOIRES 32 A 128K)

Afin de répondre aux exigences du système dans lequel est implanté le module, la carte comporte un certain nombre de cavaliers sur embases et de broches à wrapper qui doivent être positionnés en fonction :

- de la capacité du module

- de l'affectation à un N° processeur

- de la zone d'adressage

- du mode de fonctionnement : interlivins ou non

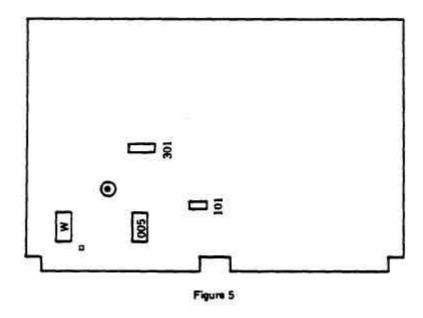

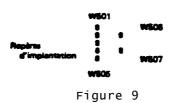

La figure ci-dessous montre l'implantation des cavaliers sur embases (005.101.301) et broches à wrapper (W)

#### 3.1 ADRESSAGE

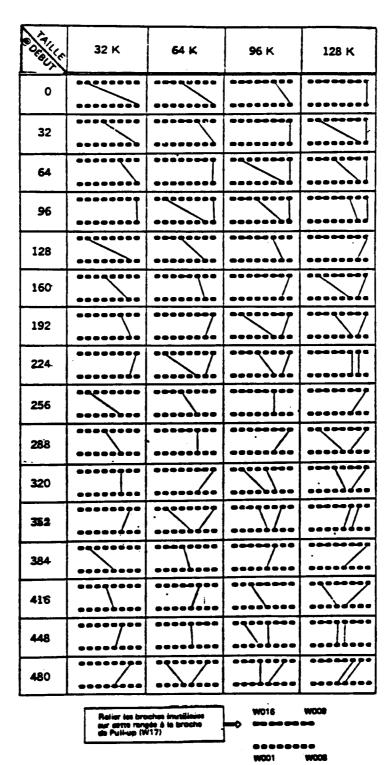

Le Principe de base est de fractionner l'espace mémoire (1 M mots) en 8 pages de 128 K et en 8 lignes de 16 K. Le circuit utilisé peut affecter n'importe quelle ligne à n'importe quelle page. Les figures 7 et 8 explicitent les cas 'standard' de sélection mémoire.

Les broches inutilisées (pour les capacités inférieures à 128 K) seront réunies à W17.

Ce circuit permet de modifier l'emplacement géographique des "lignes" de 16 K sur le circuit imprimé. Ainsi, quelle que soit l'adresse de "début" de la carte mémoire, les boîtiers resteront implantés au même endroit.

#### Exemple:

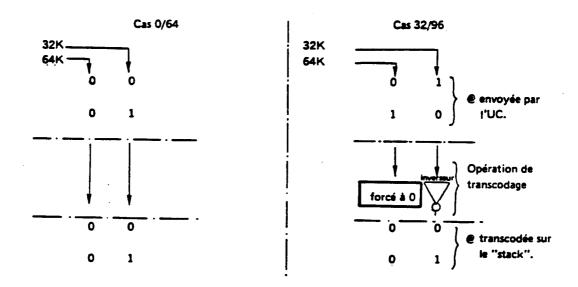

Cas d'une carte 64 K implantée de 0 à 64 K qui serait translatée de 32 à 96 K. Comme la capacité reste la même, il serait regrettable d'avoir à déplacer les boîtiers de RAM. Une autre solution consiste à modifier l'adresse de ligne :

Figure 6

Ainsi, en inversant ou en forçant à 0 un des 2 (ou les 2) bits d'adresse ayant pour poids 32 et 64 K on arrive à réaliser la fonction demandée. Il faut noter cependant que ce circuit ne fonctionne que pour des groupes de 32 K. Le câblage est indiqué dans la figure 9.

#### 3.3 MODE NORMAL - SANS INTERLIVING.

Positionnement des cavaliers sur embases Figure 10.

#### 3.4 "INTERLIVING"

Ce mode de fonctionnement permet, dans le cas ou on dispose de plusieurs mémoires, d'entrelacer les demandes de cycle. Par exemple, pour un "interliving" d'ordre 2, les adresses paires sont 'vues' par une mémoire, les impaires par l'autre. L'occupation des circuits d'une carte est alors réduite de moitié, ce qui permet de réduire les temps d'attente UC (Mémoire).

## Bull !: Interling d'ordre 2

Il ne pourra fonctionner que pour des cartes COMPLETES (128 K) et dont les adresses de début seront 0,256, 512 ou 768 K. Voir figure 11 et 12.

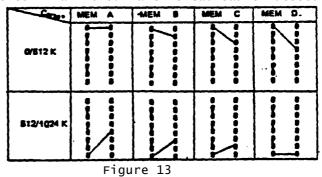

## 3.4.2 "Interliving" d'ordre 4

Comme celui d'ordre 2, il ne pourra fonctionner qu'avec des cartes complètes (128 K) et dont les adresses de début seront 0 ou 512 K. Voir figure 13 et 14.

#### 3.5 REGLAGE DU DESKEWING

Ajuster C103 et agir sur le commutateur CR1 (104) de façon à obtenir un décalage de 35 + -5 ns entre : CLK (A34) et TP (A32). (Front de montée).

Figure 7

Figure 8

## CABLAGE DE W501 A W507

- POSITIONNEMENT DES CAVALIERS SUR EMBASES 005 A 101

- Fonctionnement sans interliving

Figure 10

- INTERLIVING D'ORDRE 2

- 1. Câbler les broches à wrapper W1 à W16 suivant le tableau ci-dessous

| Targe         | 0/256 K | 256/512 K | 512/640 K | 640/1024 K |

|---------------|---------|-----------|-----------|------------|

| MÉMOIRE<br>A' |         |           |           |            |

| MÉMOIRE<br>B* | 7       |           |           |            |

Figure 11

2. Positionner les cavaliers sur embases 005 et 101 comme suit

Figure 12

- INTERLIVING D'ORDRE

- 1. Câbler les broches w1 à w16 suivant le tableau ci-dessous

2. Positionner les cavaliers sur embases 003 et 101 comme suit

Figure 14

<sup>\*</sup> les quatre cartes deviennent indissociables.

## 3.6 . INSTALLATION ET RACCORDEMENT

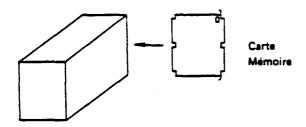

#### Sans option

## Avec option : Batterie de 0,5 AH

## Avec option : Batterie de 1,2 ou 7 AH

Figure 15

Le module mémoire en place, sera testé à l'aide du programme de test mémoire N° 1 158 232 00.

## 4 PRESENTATION (MEMOIRES 128 K A 512 K)

### 4.1 BUT

La mémoire vive à semi-conducteurs est destinée à stocker les informations "Instructions" ou "opérande" relatives à un ou plusieurs Processeurs des Types SOLAR 16-40, 16-65, 16-75, 16-85 ou IDP.

Les mots stockés ont une longueur de 17 bits (16 bits d'information et 1 bit de parité). Le bit de parité est élaboré et contrôlé par le processeur.

#### 4.2 CONSTITUTION DES MODULES.

Ces mémoires dites "128 K à 512 K" se répartissent en 3 modules.

| CAPACITE | N° DU MODULE | CONSTITUTION                         |

|----------|--------------|--------------------------------------|

| 128 K    | 1 159 237 03 | 1 150 266 03     Carte Mémoire 128 K |

|          |              | 1 153 064 04 Cable batterie          |

| 256 K    | 1 159 237 02 | 1 150 266 02 Carte Mémoire 256 к     |

|          |              | 1 153 064 04 Cable batterie          |

| 512 K    | 1 159 237 01 | 1 150 266 01     Carte Mémoire 512 к |

|          |              | 1 153 064 04 Cable batterie          |

### 4.3 CONTRAINTES DE CONFIGURATION

La carte est enfichable dans les bacs de hauteur :

12 U = Cartes verticales

6 U = Cartes horizontales

4 U = Cartes horizontales.

Bull

## 4.4 CONTRAINTES D'UTILISATION

## 4.4.1 Environnement

- Température 0°C <= T <= 40° C

- Humidité : <= 90 % sans condensation

- Chocs et vibrations : compatible avec les équipements électroniques standard.

Des précautions doivent être prises lors des manipulations des cartes notamment pour le pot en ferrite de l'alimentation.

## 4.4.2 Caractéristiques électroniques

Consommation sur tension bac.

AU REPOS A CADENCE MAX

5V 2A 2A

24V 0,4A 0,5A

Consommation sur batterie de sauvegarde

16 V 0,5 A

Utilisation en mono processeur :

Figure 16

TC = Temps de cycle = 5 C LK (lecture, écriture ou échange)

TA = Temps d'accès = 3 C LK (lecture ou échange)

Utilisation en multi-Processeur :

Figure 17

TC = 4 C LK (lecture, écriture ou échange)

TA = 3 C LK (lecture ou échange)

Remarque importante :

Les boîtiers mémoires MOS utilisés sur le module sont du type dynamique, de ce fait, il est nécessaire de rafraîchir l'information contenue en mémoire. Une horloge interne déclenche toutes les  $14\mu s$  un cycle de rafraîchissement qui dure 30 LK. Si un processeur demande à ce moment un accès à la mémoire, cet accès est retardé jusqu'à la fin du rafraîchissement en cours. Ce qui allonge d'autant la durée de l'accès et du cycle demandé. Théoriquement, la mémoire étant occupée 2 % de son temps à faire des rafraîchissements, il convient d'ajouter 2 % à la durée moyenne d'un accès. Pratiquement, à cause d'une resynchronisation partielle des demandes de cycle simultanées, cette augmentation de durée peut être estimée à 1 %, donc d'une influence négligeable sur les performances du système.

Pour assurer la sauvegarde de l'information contenue en mémoire, en cas de coupure des alimentations du bac, le module peut être équipé de batteries.

Module 0,5 AH

ou Module 1,2 AH N° 1 159 111 01 ou Module 7 AH N° 1 159 111 03

Le module 0,5 AH est enfiché directement sur les connecteurs avant de la carte mémoire.

Les modules : 1,2 AH, ou 7 AH sont placés dans le bac et sont raccordés sur un bornier situé à l'avant de la carte mémoire par un câble.

## Bull 🏥

#### 5 FONCTIONNEMENT DU MODULE MEMOIRE

## (MEMOIRES 128K A 512 K)

#### 5.1 GENERALITES

Le module mémoire dialogue avec le ou les processeurs auxquels il est affecté par l'intermédiaire du bus mémoire (Voir Notice N $^\circ$  1 160 902 00).

La mémoire est constituée à base de boîtiers RAM (64K dynamiques 16 broches de temps d'accès à la lecture 200 ns).

Un synoptique du module est représenté sur la figure 18.

Le module peut effectuer trois types de cycles Lecture, Écriture et Echange.

#### 5.2 PRINCIPE DE FONCTIONNEMENT

On peut diviser le module en deux parties principales :

- A) Circuits de dialogue avec le bus I/O

- L'interface de contrôle : elle assure le dialogue avec le bus mémoire (si mémoire occupée : section de la file d'attente, rappel du processeur en attente, etc...), le chargement des registres "adresse" et "informations à écrire", le lancement d'un cycle mémoire à la base de temps et l'émission des infos lues sur le bus mémoire lorsque la base de temps lui indique que le cycle est terminé.

- 2) Les différents registres du module : adresse, information à écrire, information lue

- 3) Les drivers et récepteurs de bus (ne sont pas représentés sur le synoptique).

Toute cette partie synchrone est alimentée directement à partir des tensions du bac, car son fonctionnement est inutile à la sauvegarde des informations stockées.

- B) Une partie "mémoire" comprenant :

- b-1) Le stock mémoire avec ses circuits de décodage et drivers associés (non représentés).

- B-2) La logique de rafraîchissement, le compteur de rafraîchissement la surveillance d'horloge et le multiplexeur d'adresses. Ces circuits assurent les séquences et les commandes nécessaires au bon fonctionnement du stock mémoire.

## BUS MEMOIRE OUT ET COMMANDES

**BUS MEMOIRE IN**

Figure 18

Bull

Ces circuits sont alimentés par une alimentation secourue située sur la carte et fonctionnent suivant l'état du système d'alimentation soit à partir du + 24 V bac, soit de la tension batterie (Option) la commutation étant entièrement automatique.

#### 5.3 SAUVEGARDE MEMOIRE

La sauvegarde de l'information est assurée, en option, par un système de batteries Cadmium - Nickel de capacité 0,5 à 7 AH. Pour les temps de sauvegarde consulter le manuel d'utilisation des "batteries". 1 159 110 ID 30.

Un synoptique du système d'alimentation est représenté sur la figure 19.

Un voyant implanté sur l'avant des cartes mémoire permet de vérifier la tension de la batterie. Il s'éteint lorsque la tension aux bornes de la batterie tombe en dessous de 15 volts'.

Figure 19

## 6 MISE EN ŒUVRE. POSITION DES CAVALIERS SUR EMBASES (MEMOIRES 128K A 512K)

Afin de répondre aux exigences du système dans lequel est implanté le module, la carte comporte un certain nombre de cavaliers sur embases qui doivent être positionnés en fonction :

- de la capacité de la carte --> positionnement en fabrication

- de l'affectation à un numéro de processeur

- de la zone d'adressage Mode normal

- de la zone d'adressage Mode Interliving d'ordre 2.

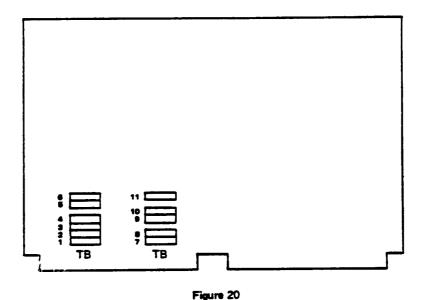

Emplacement des embases.

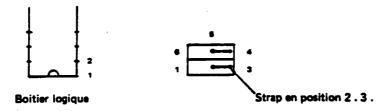

Les cavaliers sur embases sont représentés toujours dans ce sens.

Figure 21

Ce Positionnement est effectué en fabrication.

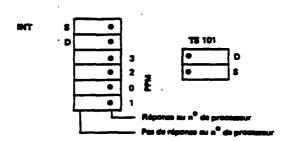

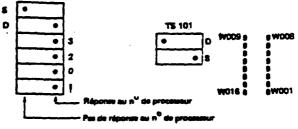

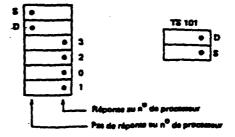

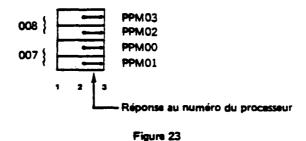

6.2 AFFECTATION A UN NUMERO DE PROCESSEUR (TB 007 . TB 008)

6.3 ZONE D'ADRESSAGE MODE NORMAL.

### 6.3.1 Mode normal pour toutes VU

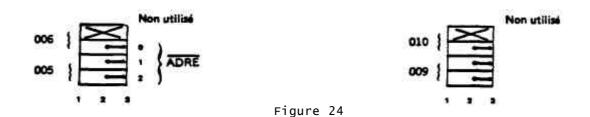

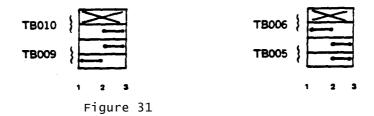

TB005. TB006. TB009. TB010

## 6.3.2 Mode normal Zone d'adressage

TB001. TB002. TB003. TB004

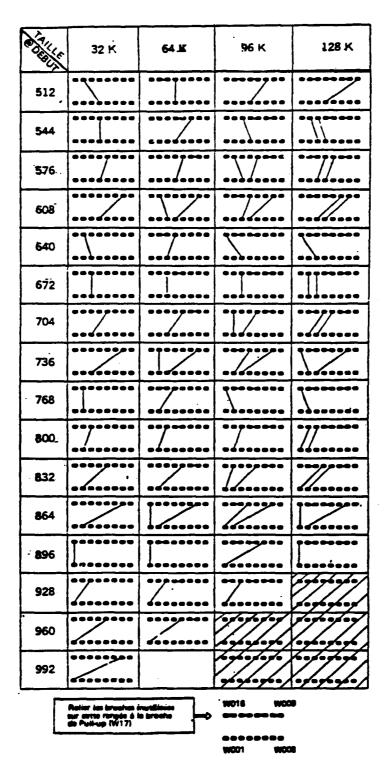

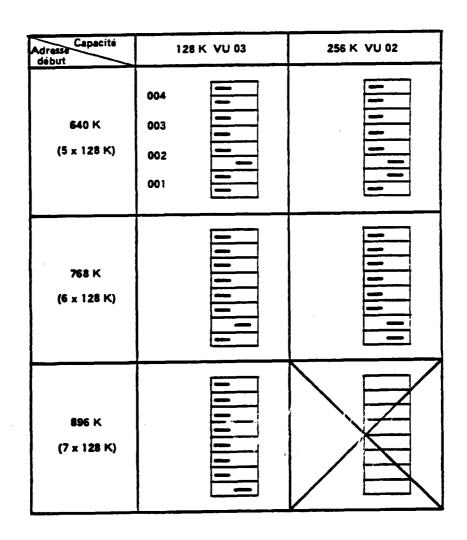

Les zones d'adressage commencent sur une frontière de 128 K pour toutes les VU.

| Adressa Capacité<br>début | 128 K YU 03                        | 256 K VU 02 | 512K VU 01 |

|---------------------------|------------------------------------|-------------|------------|

| 0                         | TB 004 } TB 003 } TB 002 } TB001 } |             |            |

| 128 K                     |                                    |             |            |

| 256 K                     |                                    |             |            |

| 384 K                     |                                    |             |            |

| 512 K                     |                                    |             |            |

Figure 25

Figure 26

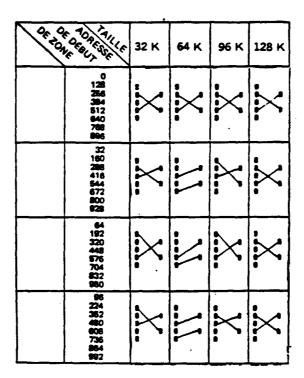

Le mode Interliving permet d'associer 2 cartes mémoire, de même capacité, en les sélectionnant par le bit poids faible d'adresse. Ainsi la première carte répond aux adresses paires et la deuxième aux adresses impaires.

Le temps de cycle apparent en écriture est alors divisé par 2. (2 CLK au lieu de 4 CLK).

## 6.4.1 <u>Interliving avec 2 cartes 1.150 266 03 (128K)</u>

- Permutation de ADR2 et MOUT15. Positions des TB 005, 006, 009, 010 identiques sur les 2 cartes.

Figure 27

- Zone d'adressage

Les zones d'adressage commencent sur une frontière de 256 K

| Adresse<br>début                          | 0        | 256 K | \$12 K | 768 K |

|-------------------------------------------|----------|-------|--------|-------|

| lère carte<br>128 K<br>Adresses<br>peires | TB 004 } |       |        |       |

| 2ème carte 128 K Adresses Impaires        |          |       |        |       |

Figure 28

Bull

## 6.4.2 <u>Interliving avec 2 cartes 1 150 266 02 (256 K)</u>

- Permutation de ADRE1 et MOUT15. La position des TP 005, 006, 009, 010 est identique sur les 2 cartes du couple.

Figure 29

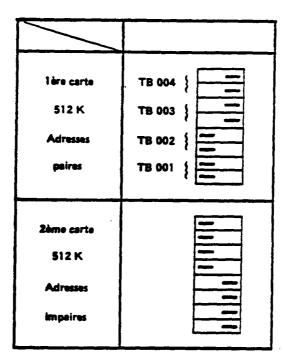

- Zone d'adressage

Les zones d'adressage commencent sur une frontière de 512 K.

| Adresse<br>début                            | O                                            | 512 K |

|---------------------------------------------|----------------------------------------------|-------|

| lère carte  256 K  Adresses  peires         | TB 004 } = = = = = = = = = = = = = = = = = = |       |

| 2ème carte<br>256 K<br>Adresses<br>impaires |                                              |       |

Figure 30

## Bull erliving avec 2 cartes 1 150 266 01 (512K)

- Permutation de ADREO et MOUT 15 La position des cavaliers sur embases 005, 006, 009, 010 est identique sur les 2 cartes.

- Zone d'adressages 0 à 1024 K

Figure 32

## 6.5 REGLAGE DU DESKEWING

CLOCK (A 34) et TP (A 32).(Front de montée). Ajuster CX et agir sur le commutateur (emplacement 104) de façon à obtenir un décalage de 35 +- 5NS entre le signal : CLOCK (A34) et TP (A32) (Front de montée).

## Bull

## 6.6 INSTALLATION ET RACCORDEMENT

Sans option

## Avec option : Batterie de 0.5 AH

### Avec option : Batterie de 1,2 ou 7 AH

Figure 33

Le module mémoire en place, sera testé à l'aide du programme de test mémoire N° 1 158 232 00.