Constitution

n° module 1.159.233 comprenant 1 carte 1.150.262.01 (format 1/1 consommation < 8A,5V) 1 manuel d'exploitation 1.159.233 ID46 1 programme de test 1.158.233

Raccordement

Utilise un emplacement Bus Mémoire

But du module

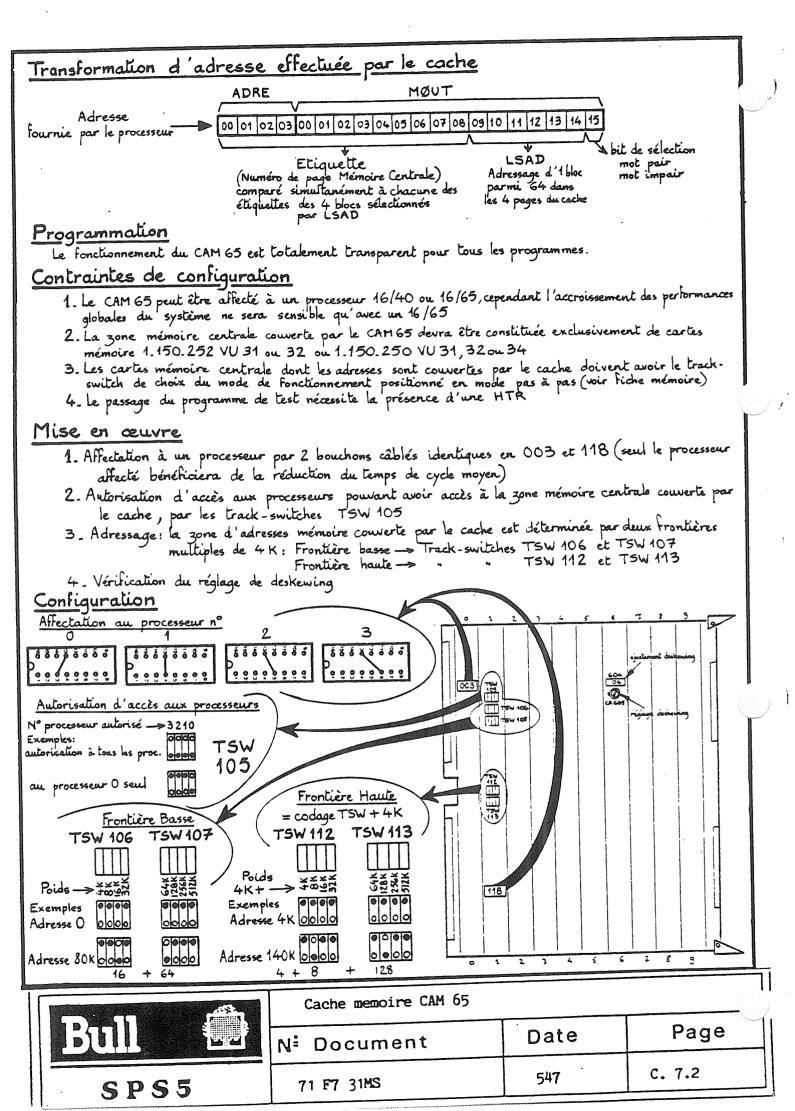

Le CAM 65 est un module mémoire rapide de capacité 512 mots de 17 bits, temps de cycle 375 ns, temps d'accès 125 ns. Le CAM 65 se superpose à la mémoire centrale (temps de cycle 750 ns) dont il contient à tout instant une copie de 512 mots organisée en 64 fois 4 zones de 2 mots appelées "blocs". La partie de la mémoire centrale dont le contenu des adresses est susceptible d'être dupliqué dans le cache est appelée zone d'adresses "couverte" par le cache.

Le CAM 65 est affecté à un processeur UC (généralement le processeur O). Lorsqu'une lecture en mémoire est demandée par le processeur, l'adresse est reçue simultanément par le cache et par la mémoire. Si l'information est présente dans le cache, elle est émise vers le processeur en mode H5M (temps de cycle 375 ns) et le cycle en mémoire principale est interrompu (Abort). Si l'information n'est pas présente dans le cache, le cycle de lecture en mémoire principale se déroule normalement et, lors du retour de l'information lue, le cache stocke cette information afin de pouvoir répondre à une prochaine demande de lecture à cette adresse. Lorsqu'une écriture est effectuée par un processeur quelconque à une adresse connue du cache, l'écriture est faite simultanément dans le cache et dans la mémoire principale. Du fait qu'à un instant donné, le programme se déroule dans un certain nombre de boucles relativement petites, 80 à 95% des demandes de lecture seront satisfaites par le cache et le temps de cycle moyen variera de 400 à 475 ns alors que le temps de cycle de la mémoire centrale est de 750 ns. L'attribution des blocs disponibles dans le cache est effectuée automatiquement selon l'algorithme LRU (Least Recently Used), c'est à dire que lors d'une demande de lecture à une adresse inconnue du cache, celui-ci sélectionnera parmi les localisations possibles dans le cache celle qui a été utilisée le moins récemment, détuuira son contenu et le remplacera par la nouvelle information et remettra à jour le LRU du bloc dans lequel on vient d'écrire (LRU=00) et le LRU des 3 autres blocs adressés par LSAD (voir ci-dessous).

Organisation des informations dans le cache

Le CAM 65 est organisé en 4 pages de 64 blocs. Les blocs de la page O sont appelés blocs O, les blocs de la page 1 blocs 1, etc... Composition d'un bloc: 2 mots de 17 bits correspondent à des adresses paires et impaires 1 bit de validation par mot (information présente ou non) 13 bits d'étiquette (poids forts d'adresse)

2 bits LRU (valeur 0 à 3 suivant l'ancienneté de la dernière demande d'accès au bloc)

|                                              | 64<br>blocs | Mot Adresse paire | bit de validation paire  Mot Adresse impaire | bit de validation impaire page  Etiquette LRU bloc 0 | 0              |

|----------------------------------------------|-------------|-------------------|----------------------------------------------|------------------------------------------------------|----------------|

| Adressage<br>d'16loc<br>parmi 64<br>par LSAD | 64 blocs    |                   |                                              | bloc 1 } page                                        | 4              |

|                                              | 64 blocs    |                   |                                              | bloc 2 page                                          | . 2            |

|                                              | 64<br>bloss |                   |                                              | bloc 3 page                                          | <sub>2</sub> 3 |

| B |   |   |   |   |   |  |

|---|---|---|---|---|---|--|

|   | S | p | S | 5 | ı |  |

| Cache | memoire | CAM | 65 |

|-------|---------|-----|----|

|-------|---------|-----|----|

| Nº Document | Date | Page   |

|-------------|------|--------|

| 71 F7 31MS  | 547  | C. 7.1 |